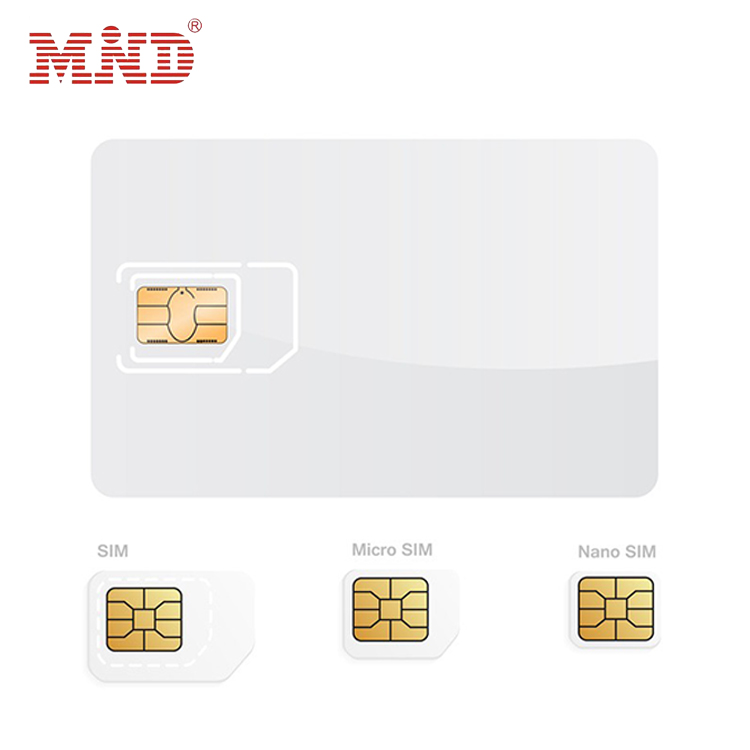

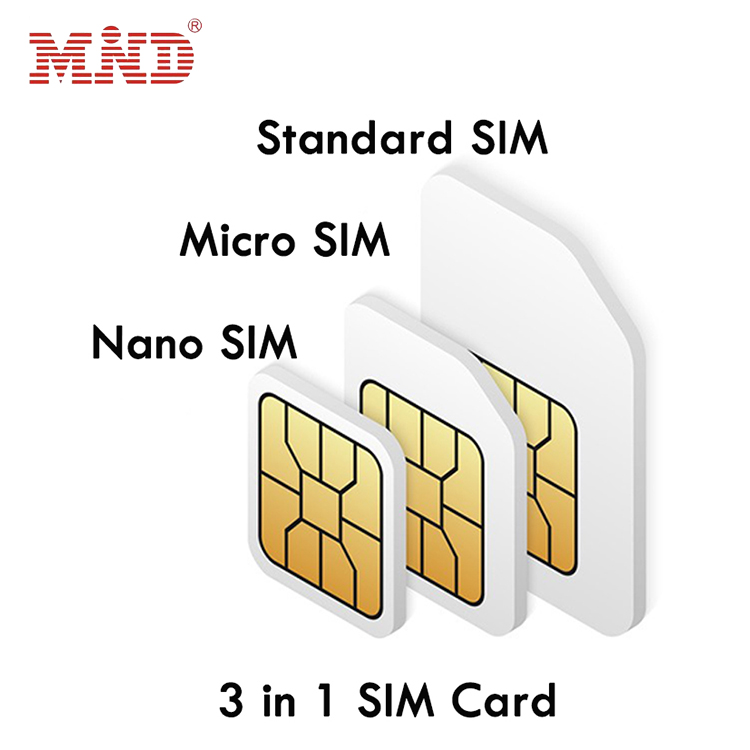

THC80F480A SIM Applikatioun 6pin 8pin 4FF Kontakt Smart Card IC Chip SIM Kaart

Beschreiwung

Den THC80F480A ass eng Kontakt-Smartcard-IC mat enger 32-Bit CPU, 480 KB FLASH an Hardware-TRNG/CRC.

D'Entwéckler kënnen de Späicher a verschidde Gréissten opdeelen.

Déi seriell Interface ISO/IEC 7816-3 ënnerstëtzt den T=0 /T=1 Protokoll an 11 Baudraten.

Fir besser Sécherheet a Zouverlässegkeet ënnerstëtzt de Chip vill Hardware-Sécherheetsfeatures, z.B. Héich-/Niddregspannungs- an Héich-/Niddreg-Taktfrequenzdetektoren, asw.

Den THC80F480A ass gëeegent fir allgemeng IC-Kaartenapplikatiounen, wéi SIM, Pay-TV Kaart, Campus Kaart, City Kaart, etc.

Spezifikatiounen

| Symbol | Numm | Konditiounen | Min. | Typesch | Max | Eenheet |

| TPE | Zäit fir eng Säit ze läschen | - | 2 | 2,5 | 3 | ms |

| TBP | Zäit fir e Programm e Byte | - | 33 | 37 | 41 | μs |

| TDR | Datespäicherung | - | 10 | - | - | Joer |

| NPE | Säitenausdauer | - | 100000 | - | - | Zyklus |

| fEXT | Extern Auerfrequenz | - | 1 | - | 10 | MHz |

| fINT | Intern Auerfrequenz | - | 7,5 | - | 30 | MHz |

| Vcc | Versuergungsspannung | - | 1,62 | - | 5.5 | V |

| Icc | Versuergungsstroum | Vcc=5,0V | - | 5 | 10 | mA |

| Vcc=3,0V | - | 4 | 6 | mA | ||

| Vcc=1,8V | - | 3 | 4 | mA | ||

| ISB | Standby-Stroum (Auerstopp) | Vcc=5,0V | - | 70 | 200 | μA |

| Vcc=3,0V | - | 60 | 100 | μA | ||

| Vcc=1,8V | - | 50 | 100 | μA | ||

| TAMB | Ëmgéigungstemperatur | - | -25 | - | 85 | °C |

| VESD | ESD-Schutz | HBM | 4 | - | - | kV |

CPU

CPU:

Héichleistungs-32-Bit CPU-Kär

Little Endian

Dräistufeg Pipeline

D'CPU-Betribszäit kann konfiguréiert ginn:

Intern Auer:7,5 MHz/15 MHz/30 MHz (nominal)

Extern Auer:Kontakt Smartcard-Input CLK-Versuergung iwwer C3 (ISO/IEC 7816)

Erënnerungen:

BLIZZ

Gréisst:480KB

Säitegréisst:512 Bytes

Läschen a Programméierungsoperatioun:Säitenläschen, Byteprogramm a konsekutiv Byteprogramm

Typesch Zäit:Läschen 2,5 ms/Säit, Byteprogramméierung 37 μs/Byte, Programméierung vu konsekutive Bytes 5,6 ms/Säit

Bit-Logik:1b nom Läschen, 0b nom Programméiere fir 0b ze sinn

Benotzung:Code an Daten

RAM-Gréisst:13KB

Benotzer-OTP:224 Bytes

Nummernummer:17 Bytes

Peripheriegeräter

CRC: 16-Bit CRC-CCITT TRNG: Echte Zoufallszuelengenerator, fir sécher Transaktiounen Timer: Zwee 16-Bit Timer, een ETU Timer

Schnittstellen ISO/IEC 7816-3 seriell Schnittstell UART ënnerstëtzt den ISO/IEC 7816-3 T=0/T=1 Protokoll an 11 Baudraten: F/D = 11H, 12H, 13H, 18H, 91H, 92H, 93H, 94H, 95H, 96H, 97H ISO/IEC 7816 Schnittstell DMA ETU Timer fir Nullbyte ze schécken Ënnerstëtzung vu GSM Stroumverbrauchsnormen, inklusiv Clock Stop Modus

Sécherheet Scrambling Datenspeicher Héich-/Nidderspannungs- an héich-/niddereg Taktfrequenzdetekteren CLK-Filter (ISO/IEC 7816 extern Takt)

Entwécklungs-Toolkits AK100 Emulator TMC Target Board IDE: Keil uVision3/4 Benotzerhandbuch an Applikatiounsnotizen Demoprojet an API (Application Program Interface) Coden Den UDVG Softwaretool fir COS Downloadskript am vum Benotzer gewënschte Format ze generéieren

Produktkategorien

-

E-Mail

-

Skype

-

WhatsApp

-

WeChat

WeChat

-

Uewen